Sandy Bridge

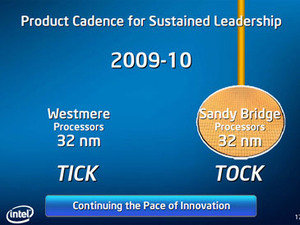

Next on the agenda was Sandy Bridge - this is Intel's next 'tock' after the Westmere 'tick' that'll be an enhanced Nehalem on a 32nm process.Back at the Intel Developer Forum Fall 2007 in San Francisco, we learned that the team for this design project had already been assembled in Israel and that it was expected to arrive late in 2010.

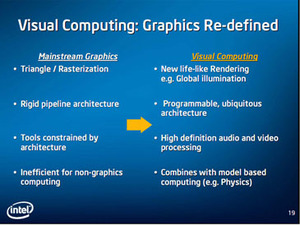

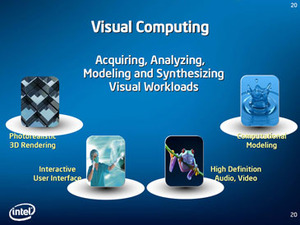

Details are thin on the ground at this early stage, but Intel said that we will see greater co-ordination between CPU and GPU from Intel when Sandy Bridge launches.

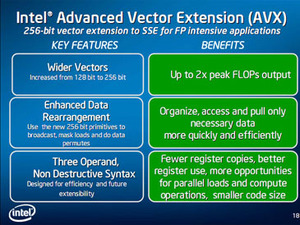

Intel revealed the first details on Sandy Bridge during the call - it will feature what Intel is calling Advanced Vector Extension.

This will be an extension to the current Intel Architecture design that will increase the size of the vector instructions from 128-bit to 256-bit. Intel says that this will allow for up to double the peak throughput (in FLOPS) in floating point intensive applications. For example, in a single add instruction current designs can operate on four single precision floating point or two double precision floating point calculations - this will be doubling to eight and four respectively with 256-bit vector extensions.

What came next is what really piqued our interest though...

MSI MPG Velox 100R Chassis Review

October 14 2021 | 15:04

Want to comment? Please log in.